Notícias

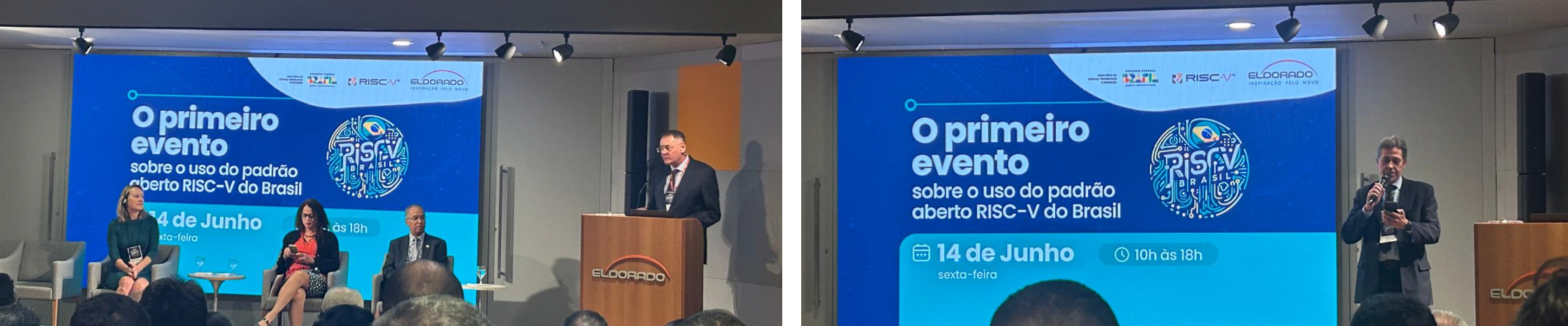

LNCC participa do primeiro evento RISC-V Brasil

Representando o LNCC, o coordenador da COTIC, Wagner Leo, e a coordenadora do SEPAD, Carla Osthoff, participaram do primeiro evento sobre tecnologia realizado no país, o RISC-V Brasil. O evento contou com a participação da Ministra de Estado da Ciência, Tecnologia e Inovação, Luciana Santos, junto com o Secretário de Ciência e Tecnologia para Transformação Digital, Henrique Miguel, ambos representando o governo federal. Eles dividiram o palco com a CEO do RISC-V International, Calista Redmond, o CEO da Ventana Micro Systems, Balaji Baktha, e o anfitrião e superintendente do Instituto Eldorado, Roberto Soboll.

Ao longo do dia, ocorreram apresentações de ICTs, universidades e empresas, trazendo suas pesquisas e desenvolvimentos usando RISC-V, além da estratégia brasileira de semicondutores, apresentada por Alessandro A. N. Campos, D.Sc.

No encerramento do evento, o Coordenador-Geral de Tecnologias Digitais do MCTI, Guilherme Corrêa, lembrou aos presentes que, em pouco mais de um ano, o Brasil saiu do quase "zero" em termos de apoio governamental ao RISC-V. Para se tornar ativo nesse ecossistema, o país tornou-se membro "premier" da associação RISC-V International, observando que, além do Brasil, somente os governos da China e Índia são membros na mesma categoria. Destacou também o desejo do MCTI para que este seja o primeiro de muitos outros eventos e que nosso ecossistema de "semicondutores, HPC e IA" se torne cada vez mais vibrante, colaborativo e soberano.

O LNCC recebeu do "RISC-V International Technical Program Manager", por meio do Rafael Sene, a doação de duas placas servidoras de RISC-V, para serem utilizadas na comunidade científica, no desenvolvimento de pesquisas e em cursos de formação na área de Semicondutores, a serem implementados na "Escola de Verão Supercomputador Santos Dumont". Conforme a apresentação feita pelo consultor sênior do MCTI, prof. Guido Araújo da UNICAMP, junto ao "RISC-V Technical Steering Committee", o domínio da tecnologia de IA está altamente relacionado com o domínio nas áreas de Semicondutores e de HPC.

Sobre o RISC-V

O RISC-V é uma arquitetura de conjunto de instruções (ISA) de padrão aberto, projetada para promover a inovação em processadores através da colaboração aberta. Essa arquitetura permite que a comunidade tecnológica compartilhe investimentos técnicos e contribua para o desenvolvimento estratégico futuro. Além disso, facilita a criação rápida de novos designs, proporciona uma liberdade de design sem precedentes e reduz significativamente os custos associados à inovação.

- Saiba mais em: https://riscv.org/