# Confecção de máscara fotolitográfica para a construção e caracterização de dispositivos do tipo transistores de filme fino

Angélica Denardi de Barros (CTI) adbarros@cti.gov.br Thebano Emilio de Almeida Santos (CTI) thebano.santos@cti.gov.br

#### Resumo

Transistores de filme finos (thin film transistors) são dispositivos frequentemente utilizados no controle dos dispositivos emissores de luz em matrizes ativas. Existe atualmente um vasto campo em pesquisa sobre estes dispositivos para o desenvolvimento destas matrizes e sua aplicação em mostradores de informação tanto rígidos quanto flexíveis. Este artigo descreve os passos para a confecção de uma máscara de fotolitografia de dispositivos do tipo TFTs e dispositivos utilizados durante o controle do processo de microfabricação dos mesmos.

Palavras-chave: TFT, AMOLED, microfabricação, fotolitografia.

# 1. Introdução

A origem dos TFTs data de 1930 quando o primeiro Transistor de Efeito de Campo (FET) foi proposto e patenteado por Lilifield que descreveu um dispositivo cujo fluxo de corrente era controlado pela aplicação de um campo elétrico transversal.

O primeiro Transistor de Filme Fino (TFT) foi criado em 1962 por Weimer nos laboratórios RCA. Neste trabalho Weimer usou uma técnica de evaporação à vácuo e máscaras de sombra para definir eletrodos de fonte e dreno de ouro, o semicondutor cristalino de sulfato de cádmio tipo-n, o dielétrico de porta de monóxido de silício e contato de porta de Au em um substrato isolante de vidro.

Alguns anos depois, em 1964 foi demonstrado o primeiro TFT em substrato transparente com óxido metálico como semicondutor e construído utilizando técnicas de fotolitografia.

Após algumas décadas, em 1996 semicondutores de óxidos metálicos ganharam atenção quando Prins et al demonstraram um TFT completamente transparente. À partir de 2003 Nomura et al construíram um TFT baseado em óxido de índio gálio e zinco (IGZO) cuja mobilidade do elétron era de  $80 \text{cm}^2 \text{V}^{-1} \text{s}^{-1}$  e a razão on/off da corrente era de  $10^6$ , demonstrando ser possível obter TFTs de alta performance com a estrutura metal óxido semicondutor. A partir de então, outros estudos permitiram ainda a obtenção de TFTs utilizando métodos de deposição à baixa temperatura e em substratos flexíveis com alta performance. Nos anos seguintes, semicondutores de óxidos metálicos multicomponentes como óxido de zinco estanho (ZTO), óxido de zinco índio e muitas maneiras de se obter IGZO foram investigadas. Hoje, o estado da arte de TFTs baseados em IGZO apresentam uma performance elétrica excelente com valores de mobilidade até  $84 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  e razão de corrente on/off acima de  $10^{10}$ , dependendo da composição do semicondutor e da configuração do dispositivo.

Existe atualmente uma literatura vasta e abundante sobre a confecção de transistores de filmes finos baseados nos mais diferentes materiais e técnicas. Para acompanhar o desenvolvimento desta tecnologia é de extrema importância o desenvolvimento de uma estrutura de testes, que se comporte como um laboratório, capaz de validar o desenvolvimento destes novos

transistores, quando confeccionados tanto com materiais tradicionais quanto com materiais inovadores. Este trabalho apresenta o desenvolvimento de uma máscara de fotolitografia para a microfabricação de dispositivos eletrônicos que permita avaliar as propriedades elétricas de novos processos e de deposição de materiais inovadores, permitindo que a caracterização elétrica traga informações que somem aos resultados das medidas estruturais destes materiais com potencial aplicação na confecção dos TFTs.

# 2. Materiais e Métodos

#### 2.A Materiais

Os primeiros transistores de filmes finos reportados eram transistores de óxidos binários como o  $SnO_2$ , o ZnO, o  $In_2O_3$  e o  $Ga_2O_3$  tanto puros quanto com impurezas dopantes. Estes materiais são caracterizados por apresentarem um largo bandgap (Eg>3eV) e uma grande transmissão na faixa do visível (acima de 80%). Nestes casos os filmes resultantes são semicondutores do tipo-n, o que fornece uma alta concentração de portadores (N) da ordem de  $10^{16} cm^{-3}$  à  $10^{21} cm^{-3}$ , o que é atribuído aos doadores nativos, por exemplo as vacâncias de oxigênio e/ou os átomos metálicos[1].

Além disso, mesmo que estes filmes se apresentem na fase amorfa, eles fornecem alta mobilidade efetiva ( $\mu FE > 10 \text{cm}^2 \text{V}^{-1} \text{s}^{-1}$ ), devido à sua estrutura eletrônica. Em contraste com os semicondutores covalentes como o Si, os óxidos metálicos semicondutores são compostos de valência com um alto grau de ionicidade entre suas ligações químicas. Em semicondutores de óxidos metálicos a transferência de carga ocorre dos orbitais s dos metais para os orbitais s dos oxigênios. O mínimo da banda de condução é de fato formado pelos altamente dispersivos orbitais metálicos desocupados, ao passo que o máximo das bandas de valência são constituídos pelos orbitais localizados e totalmente ocupados do oxigênio[2].

Estes orbitais metálicos vazios são esféricos (não possuem direção) e exibem um alto espalhamento espacial. Como consequência, o transporte eletrônico pode facilmente ocorrer através da sobreposição dos orbitais metálicos com seus vizinhos cátions metálicos. Isso explica a razão pela qual a maioria dos óxidos metálicos semicondutores fornecem uma condutividade do tipo-n e o transporte de lacunas é impedido pela alta massa efetiva.

Esta variedade de óxidos metálicos vai apresentar diferentes valores de mobilidade (dependendo da densidade de portadores e dos estados armadilhados vazios) e de  $I_{OFF}$  (quanto maior o N, maior  $I_{OFF}$  e portanto, menor é a razão  $I_{ON}/I_{OFF}$ ).

O óxido metálico mais estudado e o que apresenta a melhor performance é o ZnO que possui tanto alta mobilidade efetiva quanto alta razão  $I_{ON}/I_{OFF}$ .

A desvantagem destes materiais é que a maioria deles tende a formar estruturas poli ou nano cristalinas, o que leva a formação de defeitos por contorno de grão e uma performance não uniforme do TFT quando se trabalha com grandes áreas.

Quando comparados com compostos binários, compostos com vários componentes apresentam uma melhor performance, pois é possível obter uma fase amorfa estável quando misturados dois ou mais cátions metálicos com diferentes tamanhos e cargas iônicas, ao passo que um cátion metálico estabilizador pode ser utilizado para controlar a concentração de portadores. Por exemplo, o IZO apresenta uma fase amorfa estável, o que resulta em TFTs com uma boa uniformidade e mobilidade, entretanto, devido à alta concentração de portadores, possui uma baixa razão I<sub>ON</sub>/I<sub>OFF</sub>. Já o IGO, devido às fortes ligações do Ga com o

$O_2$ , possui uma baixa densidade de portadores, mas ao mesmo tempo uma baixa mobilidade. Desta forma, Nomura e colaborados, buscando obter um óxido metálico com alta mobilidade e alta razão  $I_{ON}/I_{OFF}$  introduziram o Ga no IZO, desenvolvendo o IGZO que é hoje o óxido metálico mais utilizado. O TFT de IGZO apresenta  $\mu_{EFE}$  superior à  $10~\text{cm}^2\text{V}^{-1}\text{s}^{-1}$  com N inferior à  $10^{17}\text{cm}^{-3}[3]$ .

### 2.B Métodos de microfabricação

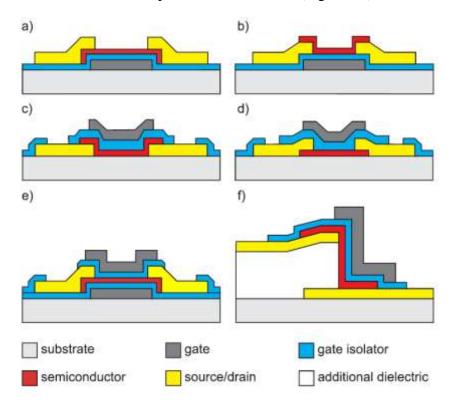

O método de fabricação também possui um importante efeito nas características, custos e estabilidade do transistor. Além disso, dependendo dos materiais empregados, os métodos de fotogravação devem ser ajustados para que os processos de microeletrônica sejam eficientes e entreguem a arquitetura escolhida em perfeita definição sem danificar os materiais estudados. Para que isso ocorra, diferentes arquiteturas já foram exploradas. As arquiteturas mais comuns de TFTs [2] são chamadas bottom-gate (BG, Figura 1.a e b) e top-gate (TG, Figura 1.c e d), dependendo da posição do eletrodo de porta, antes ou depois da camada ativa. Podem ainda ser divididas em staggered ou coplanar dependendo se os contatos de fonte/dreno estão do lado oposto ou do mesmo lado da interface semicondutor/dielétrico. Cada arquitetura possui vantagens e desvantagens que dependem dos materiais utilizados e dos parâmetros de processos para obtê-los. Para melhorar a performance estática (DC), TFTs com estruturas double-gate (Figura 1.e) podem ser empregadas de modo a melhorar o controle em uma larga porção do canal do semicondutor. Com a necessidade da diminuição do canal para dimensões nanométricas outras geometrias planares vem sendo desenvolvidas e exploradas como os TFTs verticais, onde o canal não é mais definido por uma etapa de fotolitografia, mas pela espessura da camada do matérial da porta ou do dielétrico (Figura 1.f).

Figura 1 - Configurações mais comuns de TFT (a) bottom-gate staggered, (b) bottom-gate coplanar, (c) top-gate staggered, (d) top-gate coplanar, (e) double gate e (f) vertical [3].

#### 2.C Métodos de caracterização elétrica

TFTs são dispositivos de efeito de campo com três terminais, cujo princípio de funcionamento é similar ao do MOSFET. A grande diferença é que no MOSFET o substrato de Si monocristalino é, também, a camada ativa, e, portanto, os processos envolvidos na obtenção dos dispositivos são caros, complexos e necessitam de alta temperatura (>1000°C), como por exemplo, difusão, implantação de dopantes, litografias e corrosão. Enquanto que os TFTs são geralmente fabricados em substratos isolantes (vidro ou plástico), sobre os quais as camadas dos dispositivos precisam ser depositadas em baixa temperatura (<650°C) por vácuo ou por técnicas de deposição utilizando soluções. Em função disso, as camadas ativas dos TFTs são tipicamente policristalinas ou amorfas acarretando um reduzido transporte de cargas (quando comparado ao silício monocristalino). Assim como no MOSFET, o TFT também é composto por uma camada dielétrica disposta entre um semicondutor e um contato metálico de porta, além de dois contatos de fonte e dreno depositados diretamente sobre o semicondutor. A modulação da corrente no semicondutor entre os contatos de fonte e dreno se dá através da injeção capacitiva de portadores próximos da interface entre o dielétrico e o semicondutor.

Apesar do MOSFET e do TFT dependerem do efeito de campo para modular a condutância na camada ativa, nos TFTs esta modulação ocorre na acumulação, e não na região de inversão como nos MOSFETs.

As características de performance mais importantes são extraídas da curva de corrente versus tensão (I-V). Das curvas características  $I_D$ - $V_{GS}$  e  $I_D$ - $V_{DS}$  são extraídos os parâmetros de mobilidade de portadores, tensão de limiar, razão de corrente on/off, a tensão de sub-limiar e a resistência de contato [4].

A mobilidade de portadores de efeito de campo (µFE) descreve a eficiência no transporte de portadores de cargas no material, que afeta diretamente a corrente de dreno máxima e a frequência de operação (chamada frequência de transito  $f_T$ ) do dispositivo. As maiores mobilidades encontradas dizem respeito ao silício policristalino e aos semicondutores de óxidos metálicos. Atualmente os óxidos metálicos apresentam alto custo na fabricação devido à escassez do elemento índio e da localização global de suas fontes. Apesar da disponibilidade do Si, o processo de fabricação do Si-policristalino também é relativamente caro, devido ao custo das etapas de pós-deposição necessárias em aplicações em grande área.

Em um TFT o transporte de carga está limitado a uma estreita região perto da interface dielétrico de porta/semicondutor e sofre a influência de algumas fontes de espalhamento, como o espalhamento Coulomb das cargas do dielétrico, dos estados da interface e da rugosidade da superfície da interface.

A tensão de limiar ( $V_{TH}$ ,  $treshold\ voltage$ ) corresponde à tensão de porta-fonte na qual um canal condutor é formado na interface entre o dielétrico e o semicondutor. Ela é obtida mais comumente pela extrapolação linear da curva  $I_D$ - $V_{GS}$ .

A razão on/off de corrente ( $I_{ON}/I_{OFF}$ ) é extraída da curva de transferência ( $I_{D}$ - $V_{DS}$ ) dividindo a corrente máxima pela corrente mínima de dreno (tipicamente no regime de saturação) sendo que uma razão superior à  $10^6$  é desejável.

A tensão de sub-limiar é uma medida que informa quão eficientemente um transistor passa do estado *on* para o estado *off*. Ela se relaciona diretamente com a qualidade da interface dielétrico/semicondutor. Este parâmetro é definido como o inverso da inflexão máxima do gráfico I<sub>D</sub>-V<sub>GS</sub> e indica a tensão de porta-fonte necessária para aumentar em uma década e corrente de dreno. Uma tensão de sub-limiar inferior à 100mV/dec (junto à uma tensão de

limiar próxima de 0V) é desejável para reduzir o consumo de potência e a tensão de operação em aplicações em circuitos.

A resistência de contato (RC) que depende dos eletrodos de fonte/dreno, da interface metal/semicondutor e da área de contato entre fonte/dreno e porta é um importante parâmetro que indica a possibilidade de degradação da mobilidade de efeito de campo e da frequência de trânsito dos dispositivos ( $f_T$  quantifica a velocidade de operação do dispositivo), especialmente aqueles de canal curto. Ela é obtida pelo método de linha de transmissão, que requer a análise de uma série de curvas  $I_D$ - $V_{GS}$  de TFTs com diferentes comprimentos de canal.

Além da resistência de contato, outro parâmetro que influência a frequência de trânsitos dos TFTs é a capacitância resultante da sobreposição que ocorre entre o contato de porta e os eletrodos de fonte/dreno, e, pode ser obtida das curvas capacitância-tensão (C-V).

#### 3. Resultados

A partir dos conteúdos estudados, foi escrita uma máscara para ser utilizada na construção e avaliação dos TFTs utilizando as técnicas de fotoligrafia existentes na micro e nanofabricação de dispositivos. O software utilizado para o desenho das máscaras é o Klayout. Os TFTs foram construídos respeitando regras de projetos já existentes para garantir que durante o processo de alinhamento das máscaras os padrões estejam de fato dentro das regiões propostas[5]. Desta forma, existe um espaço de pelo menos 2µm entre o desenho do limite de uma estrutura em relação à qualquer estrutura adjacente. Isso permite que erros devidos aos processos de alinhamento, revelação e corrosão dos materiais estudados não influenciem os resultados de uma forma negativa, inutilizando o dispositivo. Outro cuidado tomado, foi garantir que o primeiro nível de fotogravação consistisse em um nível específico para gerar a primeira marca de alinhamento, com um material visível, espesso e que não reaja com os processos subsequentes. Esta primeira etapa é muito necessária uma vez que a maioria dos materiais trabalhados serão transparentes.

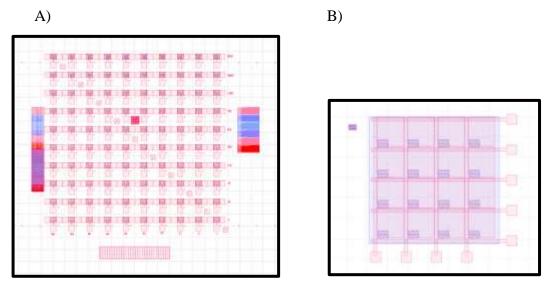

Figura 2 - Máscara para processo de microeletrônica. A) Layout completo. B) Detalhe da matriz desenvolvida.

A Figura 2 exibe o layout da máscara desenvolvida que engloba 6 níveis de processo para a confecção de transistores, diodos, capacitores, teste de resistores, marcas de alinhamento e uma matriz de transistores para teste inicial (Figura 2.B). As máscaras ainda devem ser escritas em quartzo para contemplar todas as dimensões de estruturas desenvolvidas.

Os transistores foram projetados com comprimento L variando de 1  $\mu$ m à 150  $\mu$ m e largura W variando de 1  $\mu$ m à 500 $\mu$ m. As etapas de processo consistem em: 1) definição de marcas de alinhamento, 2) contatos de fonte e dreno, 3) semicondutor, 4) dopagem de semicondutor, 5) óxido de porta e 6) contato de porta.

Foram estudados anteriormente pela bolsista os seguintes materiais: óxido de silício obtidos por sol-gel, oxido de silício dopado tipo p e tipo n obtidos por sol-gel para serem utilizados como fonte de dopantes (o desenvolvimento destes materiais está sendo mais especificamente estudado pela pós-doutoranda Ana Paula M. M. Monteiro para a eliminação de fontes de contaminação provenientes da síntese e aprimoramento das características do materiais), SnO<sub>2</sub>:F durante o auxílio na formação e supervisão do trabalho do aluno Willian Viscardi dos Anjos, e, atualmente, no desenvolvimento do ZnO:Li.

#### 4. Conclusão

O projeto atinge as expectativas do desenvolvimento de um roteiro passo a passo para a confecção e caracterização elétrica de um TFT. Além disso, o passo a passo apresentado dever ser utilizado como auxílio no esclarecimento de outros projetos similares, tendo desta forma o objetivo de servir como base estrutural. Em uma próxima etapa o presente trabalho deve ser desenvolvido experimentalmente nas dependências do CTI.

## 5. Agradecimentos

Os autores agradecem a COLAB pelo uso da infraestrutura laboratorial e ao CNPq pelo suporte financeiro.

#### Referências

- [1] Y. Kuo, "Thin Film Transistor Technology—Past, Present, and Future," *Electrochem. Soc. Interface*, pp. 55–61, 2013.

- [2] X. Yu, T. J. Marks, and A. Facchetti, "Metal oxides for optoelectronic applications," *Nat. Mater.*, vol. 15, no. 4, pp. 383–396, 2016.

- [3] L. Petti *et al.*, "Metal oxide semiconductor thin-film transistors for flexible electronics," *Appl. Phys. Rev.*, vol. 3, no. 2, p. 021303, Jun. 2016.

- [4] A. C. Arias *et al.*, "All jet-printed polymer thin-film transistor active-matrix backplanes," *Appl. Phys. Lett.*, vol. 85, no. 15, pp. 3304–3306, 2004.

- [5] L. T. Manera, "Determinação de Regras de Projeto e de Parâmetros de Simulação de um Processo nMOS para Fabricação de Circuitos Integrados Autor: Leandro Tiago Manera," State University of Campinas, 2002.